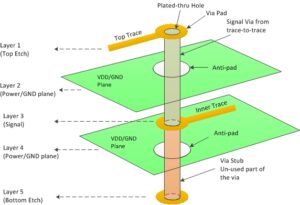

Reverse Engineering PCB Board Gerber Through Hole File will normally comes with some Side Effect, the most obvious one is the Parasitic inductance of vias;

Similarly, the parasitic inductance and the parasitic inductance of the via hole. In the reverse engineering of high-speed digital circuit board, the harm caused by the parasitic inductance of the via hole is often greater than the effect of the parasitic capacitance. Its parasitic series inductance will weaken the contribution of the bypass capacitor and weaken the filtering effect of the entire power system.

Reverse Engineering PCB Board Gerber Through Hole File will normally comes with some Side Effect, the most obvious one is the Parasitic inductance of vias;

We can use the following formula to simply calculate the approximate parasitic inductance of a via: L=5.08h[ln(4h/d)+1]

Where L refers to the inductance of the via,

h is the length of the via,

d is the diameter of the center hole.

It can be seen from the formula that the diameter of the via has little effect on the inductance, and the length of the via has the greatest impact on the inductance.

Still using the above example, the inductance of the via can be calculated as:

L=5.08×0.050[ln(4×0.050/0.010)+1]=1.015nH.

If the rise time of the signal is 1ns, then its equivalent impedance is: XL=πL/T10-90=3.19Ω.

Such impedances can no longer be ignored when passing high-frequency currents. It is important to note that the bypass capacitor needs to pass through two vias when reversing circuit card power layer and redraw printed circuit board gerber ground layer, so that the parasitic inductance of the vias will increase exponentially.