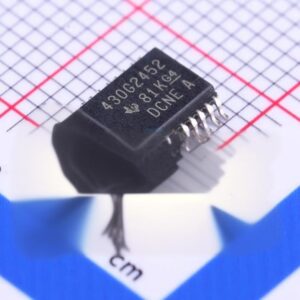

Restoring Secured MSP430G2452 Microcontroller Flash Firmware needs to break locked mcu msp430g2452 protection and then recover embedded heximal file from msp430g2452 microprocessor flash memory;

Restoring Secured MSP430G2452 Microcontroller Flash Firmware needs to break locked mcu msp430g2452 protection and then recover embedded heximal file from msp430g2452 microprocessor flash memory;

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts. Interrupt flag bits are set when an interrupt condition occurs when reverse engineering power inverter circuit board design file, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

restaurar o firmware incorporado da memória flash do TEXAS INSTRUMENT MSP430G2452 microcontrolador protegido precisa quebrar o bit de fusível de proteção MSP430G2452 MCU bloqueado e, em seguida, extrair dados binários incorporados ou arquivo heximal, em seguida, copiar o firmware para a nova memória flash do microprocessador MSP430G2452 criptografado;

The program counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0> ® PCH). The lower exam- ple in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3> ® PCH).

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When perform- ing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary to copying pcb board of drone (each 256-byte block). Refer to the Application Note AN556, “Implementing a Table Read” (DS00556).

la restauración segura de la memoria flash del microcontrolador TEXAS INSTRUMENT MSP430G2452 el firmware integrado necesita romper el bit de fusible de protección MSP430G2452 MCU bloqueado y luego extraer los datos binarios incrustados o el archivo heximal y luego copiar el firmware a una memoria flash de microprocesador nueva MSP430G2452 cifrada;

The PIC16F688 family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.