Digital Ground Plane of PCM PC Board Cloning

The buffer register and other digital circuits should be grounded and decoupled to the Digital Ground Plane of PCM PC Board Cloning. Notice that any noise between the analog and digital ground plane reduces the noise margin at the converter digital interface. Since digital noise immunity is of the orders of hundreds or thousands of millivolts, this is unlikely to matter.

The analog ground plane will generally not be very noisy, but if the noise on the digital ground plane (relative to the analog ground plane) exceeds a few hundred millivolts, then steps should be taken to reduce the digital ground plane impedance, thereby maintaining the digital noise margins at an acceptable level. Under no circumstances should the voltage between the two ground planes exceed 300 mV, or the ICs may be damaged.

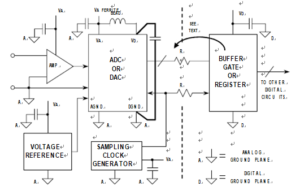

Separate power supplies for analog and digital circuits are also highly desirable. The analog supply should be used to power the converter. If the converter has a pin designated as a digital supply pin (VD), it should either be powered from a separate analog supply, or filtered as shown in the diagram. All converter power pins should be decoupled to the analog ground plane, and all logic circuit power pins should be decoupled to the digital ground plane as shown in below Figure.

Digital Ground Plane of PCM PC Board Cloning

If the digital power supply is relatively quiet, it may be possible to use it to supply analog circuits as well, but be very cautious. In some cases it may not be possible to connect VD to the analog supply. Some of the newer, high speed ICs may have their analog circuits powered by +5 V, but the digital interface powered by +3 V to interface to 3 V logic. In this case, the +3 V pin of the IC should be decoupled directly to the analog ground plane of PCM PC Board Cloning.

It is also advisable to connect a ferrite bead in series with the power trace that connects the pin to the +3 V digital logic supply. The sampling clock generation circuitry should be treated like analog circuitry and also be grounded and heavily decoupled to the analog ground plane. Phase noise on the sampling clock produces degradation in system SNR as will be discussed shortly.