Multilayer Printed Circuit Board Manufacturing main production difficulties compared with the characteristics of conventional circuit boards, high-level electronic multilayer circuit boards have the characteristics of thicker boards, more layers, denser lines and vias, larger unit size, and thinner dielectric layers. Impedance design control and reliability requirements are more stringent.

1.1 Difficulties in inter-layer alignment

Due to the large number of layers in the high-rise board, the customer design side has more and more stringent requirements on the alignment of each layer of the PCB. Usually, the alignment tolerance between layers is controlled to ±75μm. Factors such as dislocation stacking of multi-layer printed circuit board and interlayer positioning methods caused by the inconsistency of the expansion and contraction of different core board layers make it more difficult to control the interlayer alignment of high-rise boards.

Multilayer-PCB board redesign

1.2 Difficulties in making inner layers

The high-level circuit board adopts special materials such as high TG, high speed, high frequency, thick copper, and thin dielectric layer, which puts forward high requirements for the production of inner layer circuits and graphic size control, such as the integrity of impedance signal transmission, which increases the difficulty of inner layer circuit production. The line width and line spacing are small, the open and short circuits increase, the micro-shorts increase, and the pass rate is low; there are many signal layers of fine lines, and the probability of missed inspection of the inner layer AOI increases; the thickness of the inner layer core board is thin, and it is easy to wrinkle, resulting in poor exposure and etching. It is easy to roll the board when the machine is over; most of the high-level boards are system boards, the unit size is large, and the cost of scrapping the finished product is relatively high.

Multilayer Printed Circuit Board Manufacturing

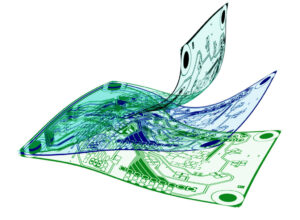

1.3 Difficulties in pressing production

Multiple inner core boards and prepregs are superimposed, and defects such as sliding plates, delamination, resin voids and bubble residues are prone to occur during lamination production. When designing the laminated structure, it is necessary to fully consider the heat resistance, withstand voltage, amount of glue filling and dielectric thickness of the material, and set a reasonable high-level multilayer pc board pressing program. The number of layers is large, and the expansion and contraction control and size coefficient compensation cannot be consistent; the interlayer insulating layer is thin, which easily leads to the failure of the interlayer reliability test. Figure 1 is a defect diagram of the cracked board delamination after thermal stress test.