The impedance value of a trace generated from Mul-tilayer PCB Circuit Board Gerber File Cloning generally depends on its line width and the distance between the trace and the reference plane. The wider the trace, the lower its impedance. In some interface terminals or pads of devices, the principle is also applicable.

When the pad of an interface terminal is connected to a high-speed signal line of PCB board reverse engineering, if the pad is particularly large at this time, and the high-speed signal line is particularly narrow, the impedance of the large pad is small, and the narrow trace must have a large impedance.

When the pad of an interface terminal is connected to a high-speed signal line of PCB board reverse engineering

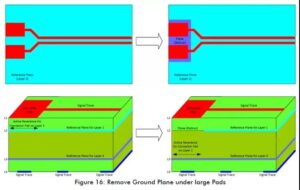

In this case, impedance discontinuity when cloning a PCB board will occur, and signal reflection will occur if impedance is discontinuous. Therefore, in order to solve this problem, a forbidden copper sheet is placed under the large pad of the interface terminal or device, and the reference plane of the pad is placed on another layer to increase the impedance to make the impedance continuous.

Mul-tilayer PCB Circuit Board Gerber File Cloning

Multilayer PCB board Vias are another source of impedance discontinuity. In order to minimize this effect, the unnecessary copper skin connected to the inner layer and the via should be removed and this kind of operation can actually be eliminated by CAD tools or contact the printed circuit board manufacturer to eliminate the unnecessary copper during printed circuit board layout redesign, and ensure the continuity of impedance.