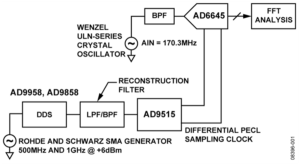

In a high performance sampled data system a low phase noise crystal oscillator should be used to generate the ADC Sampling Clock in Lambda Control Board Reverse Eng because sampling clock jitter modulates the analog input/output signal and raises the noise and distortion floor. The sampling clock generator should be isolated from noisy digital circuits and grounded and decoupled to the analog ground plane, as is true for the op amp and the ADC.

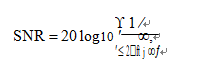

where SNR is the SNR of a perfect ADC of infinite resolution where the only source of noise is that caused by the rms sampling clock jitter, tj. Note that f in the above equation is the analog input frequency. Just working through a simple example, if tj = 50 ps rms, f = 100 kHz, then SNR = 90 dB, equivalent to about 15-bits dynamic range.

It should be noted that tj in the above example is the root-sum-square (rss) value of the external clock jitter and the internal ADC clock jitter (called aperture jitter). However, in most high performance ADCs, the internal aperture jitter is negligible compared to the jitter on the sampling clock.

Since degradation in SNR is primarily due to external clock jitter, steps must be taken to ensure the sampling clock is as noise free as possible and has the lowest possible phase jitter. This requires that a crystal oscillator be used. There are several manufacturers of small crystal oscillators with low jitter (less than 5 ps rms) CMOS-compatible outputs.