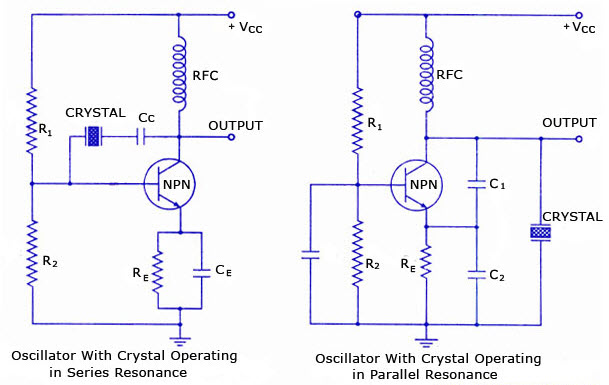

Design PCB Time Clock Component Layout has some skills which can help to optimize the PCB performance and increase the reliability of the system:

1, crystal, oscillator and related circuits should be placed in the center area of the PCB, not close to the I / O interface or board edge.

2, The clock circuit and high speed circuit should be far away from the I/O circuit area.

3, the clock circuit should keep distance from the sensitive component layout to avoid interference.

As shown in below Figure, the clock source’s filter circuit is placed as close as possible to the oscillator’s power supply input pin to minimize loop current.

clock source’s filter circuit is placed as close as possible to the oscillator’s power supply input pin to minimize loop current

4, Avoiding signal lines with long distances to be traced paralled on the same layer.

As shown in below Figure, the crystal and oscillator layout should be away from high-power components, heat sinks and other devices.

6, The crystal and crystal are as close as possible to the IC device associated with it.

7, high-speed clock circuit should be separated from the input and output device circuit 25mm, ultra-high-speed differential circuit, 10MHz or more single-ended clock circuit, reset line and other edge sensitive signals are not allowed to cross the protection area and the work area of the partition, the vulgar line should reduce non-necessary leap.

8, The crystal decoupling capacitor should be placed close to the power supply pin of the chip, and the area enclosed by the power supply and ground of the capacitor should be the smallest. It is best to use source-side matching and terminal pull-down matching.

9, the crystal oscillator power supply should be separately powered, through the magnetic beads plus capacitor filtering, the clock power supply and VCC are separated on the PCB, the same design method can be used for PLL clock distribution and other circuits.

10, Avoid crossing dense via areas or routing traces between device pins to avoid crossing planar trenches.